6��29��-30�գ��ɸ������������“2021�й������뵼���ҵ���” ¡���ٿ������λ�����ҪΧ���й�����ȱо��״����Ӧ����������ȫ���衢����оƬƽ̨�Ĵ��ơ��Զ���ʻ���������������оƬ�����Ӧ�ð��������ʰ뵼���������е�Ӧ���Լ�оƬ���Ժ��ܰ�ȫ�Ȼ���չ�����ۣ���ı��ҵδ����չ֮·�������ǹ�������Դ���������������Ĺ��ܰ�ȫ��ʦ�����ڱ��δ���ϵ��ݽ���

��������Դ���������������Ĺ��ܰ�ȫ��ʦ ����

��λ��������ã��������Թ������ĵ����顣�����������ڿƼ����ƶ��³����ĵڶ��ҹ��Ҽ������������ģ���Ҫרע������Դ�����������������㲿��������뵼�塣�ұ�����Ҫ���³���оƬ���ܰ�ȫ��صĹ�����������Ҳ���ӳ���оƬ���ܰ�ȫ�Ƕȸ���ҷ���һ�����ǵ����⡣

���������������ܻ��̶Ȳ�������������оƬ��ʹ����Ҳ�ڲ������ӡ�Ϊ�˱��Ͻ�ͨ�����ߣ�������ʻԱ�����ˡ��˿͵İ�ȫ��ҵ�ڶ���������ȫ�Ե�Ҫ��Ҳ�ڲ���������ͨ������Ҫ��оƬ����“��ȱ��”Ҫ����Ҳ�������ڳ���оƬ����һֱ���Ŀ�ꡣ�ڸ߿ɿ��ԵĻ����ϣ����ż������Ӷȵ����������ǶԳ���оƬ���ܰ�ȫ��Ҫ��Ҳ����ߣ��Ӷ������Ϳ���ϵͳ��ʧЧ�����Ӳ��ʧЧ�����ķ��ա�����оƬ�ķǹ�����Ҫ��������ɿ��ԣ�ά���ԣ������ԣ������ԣ����������ԺͰ�ȫ�ԣ����а�ȫ�������ǹ�ע���ص㡣

������о���һ��Ŀǰ�������йع��ܰ�ȫ������������緢���Ĺ��ܰ�ȫ����IEC 61508���������������������������ISO 26262��EN 50129����Բ�ͬ����Ĺ��ܰ�ȫ����������Щ����Ҳ������һЩʵ�ֲ����ָ���������Ǹ������������Ҫ����δ�Բ�ͬӦ�ý���ϸ�֡�����Ҳ�о���һЩ���ܰ�ȫ���ұ�������ʱ����Ӧ������Ҳ�ƶ��˹��ܰ�ȫ�������GB/T 34590�������к�����ڱ�����ʱ�������ͬ���⼸�������Բ�ͬ��Ӧ�ã�������ع���ϵͳ���������ϵͳ��ת��ϵͳ�ȣ��������Ӧ�Ĺ��ܰ�ȫ�����Ӷ�������أ��ƶ����ܰ�ȫ�ڹ��ڵ�ʵʩ��������Ҫע����ǣ���ISO 26262:2018����ڶ����У������˰뵼�幦�ܰ�ȫ��ص��½ڡ�����������ϸ�����˹��ܰ�ȫ�ڰ뵼������Ļ�����������ۣ����о��˲�ͬ���͵İ뵼����������Ҫ���ǹ��ܰ�ȫ�����Ҫ���ⲻ��������Ϊ�뵼���ҵ�߿���оƬʱ��ָ����ҲΪOEM��Tier1���õ�ѡ��������оƬ�ṩ�˲ο���

���ݹ��ܰ�ȫ���е�Ҫ���ܰ�ȫ����ѭ“Vģ��”���п�������֤�ģ�����“Vģ��”����������ƣ�“Vģ��”�Ҳ����������֤�Ͳ��ԡ����������оƬ����ϵͳ�����ܰ�ȫ����Ҫ��ϵͳ��ʧЧ�����Ӳ��ʧЧ���д���������ϵͳ��ʧЧͨ��ͨ����ѭһ���Ŀ�������������Ϳ��ƣ�û�ж�����ָ��ȥ�������������Ӳ��ʧЧ��ͨ����ȫ�ܹ���ƶ������̽��Ϳ��ƣ���Ҫͬʱ���㵥����϶�����DZ�����϶��������Ӳ��ʧЧĿ���ֵ��Ҫ���⣬����оƬ���ܰ�ȫӦ������ȫ�������ڹ��̣����ڲ�ͬ�ι��ܰ�ȫ��Ӧ�õ�����ʹ�ɡ�

����оƬ���ܰ�ȫ�������ѭ���ܰ�ȫ��ر�����ISO 262626�Լ�GB/T 34590���е�Ҫ������оƬ�������ԣ������ڽ��г���оƬ���ܰ�ȫ����ʱ��Ա��й涨�����̽��вü��������ʺ���оƬ�IJ��֡��ڿ��������У�������������Ҫ�ص��ע����ȫ�ܹ���ơ���ȫ���������Լ����ܰ�ȫ��֤��ȷ�ϡ���ȫ�ܹ�����ǹ��ܰ�ȫ�����ĺ��ģ�������Ҫͨ����ƺ����İ�ȫ�ܹ���ʵ�ֶ�ϵͳ��ʧЧ�����Ӳ��ʧЧ�Ŀ��ơ���ȫ��������ͨ���������������鹦�ܰ�ȫ��ƶ������Ӳ��ʧЧ��̽��Ϳ��������������ܰ�ȫ��֤��ȷ�ϻ�Թ��ܰ�ȫ���������ȷ�Ժ������Խ��м��顣

�������ǿ�һ�°�ȫ�ܹ���Ʋ��֣�����˵���Է�Ϊ�������裺��ȡ����оƬ���㰲ȫҪ��ͨ����ȫ�����Ƶ�Υ�����㰲ȫҪ���ʧЧģʽ�����ʧЧģʽ���й��ܰ�ȫ��ƣ�������ư�ȫ���ƺͰ�ȫ��ʩ�ȡ����ڶ��㰲ȫҪ����Ƶ���ͨ����˵�������ַ�������һ�ַ����ǻ����ض�Ӧ��Ҫ�����Ƶ���ȡоƬ���㰲ȫҪ��ͨ��������Ӧ�����ض�Ӧ���µ�оƬ�������ڶ��ַ����ǻ���SEooC�������ڻ����İ�ȫҪ�أ���ʽ��ȡоƬ���㰲ȫҪ�����ַ�ʽ����ʹоƬ�����ڶ���Ӧ�ã�Ҳ��Ŀǰ��Ϊ�ձ���õķ������ڵõ��˰�ȫҪ��֮����ͨ������FMEA�Լ�FTA�Ȱ�ȫ�����������Ƶ���ȡΥ����ȫҪ���ʧЧģʽ�����Υ����ȫҪ���ʧЧģʽ����Ҫ��ư�ȫ�����Լ���ȫ��ʩ���Ա�֤���ܰ�ȫҪ��õ����㡣��ȫ���Ƶ�ѡ���DZȽ���Ҫ�����ݣ���Ҫ������ASIL�ȼ�Ҫ���ϴ���ʱ�����Լ�ʵ���ѶȺͳɱ������ء�

�ڹ��ܰ�ȫ�����о���һϵ�еİ�ȫ���Ƶ�ʾ�������ǿ�����Ϊ�ο���ʹ�ã����ڴ˻����Ͻ�����չ����Ȼ��ȫ������ѡ��ʱ��Ҫ��������Ч�ԣ���Ҫ�����Ӳ��ʧЧ��ϵͳ��ʧЧ�кܺõĿ������á�����оƬ�㼶����ȫ����ͨ�������������ͣ��ڲ���ȫ���ƺ��ⲿ��ȫ���ơ��ڲ���ȫ������оƬ�ṩ������ʵ�֣�����Ҫ������Ч���ṩ֤�����ⲿ��ȫ��������оƬ����/ʹ�÷�����ʵ�ֲ���֤����Ч�ԡ����������ϸ����оƬ��ȫ�ֲ�ᷢ�֣���ʵ���ַ�ʽ�Dz���ģ�ֻʹ���ڲ���ȫ���ƻ����оƬ�ɱ������ӣ�ֻʹ���ⲿ��ȫ�����������оƬʹ���ߵĸ��������������Ŀǰ��Ӧ�õ�оƬͨ�������ڲ���ȫ���ƺ��ⲿ��ȫ����֮��ѡȡƽ��㡣���ﻹ��һ����Ҫָ�꣬���ǰ�ȫ���Ƶ���ϸ����ʣ�DC��Diagnostic Coverage��ֵ����ϸ����ʼ���˵���ǰ�ȫ���ƶ�ʧЧ��̽��̶ȣ�������ϵ�����ֵ�ĵ���ֵ֮һ99%����˵��99%��ʧЧ���Ա��˰�ȫ����̽�����ϸ�����ֵ���������ݿ��������ڱ������������ۼ���ͷ��棬Ҳ����������ר���жϣ�����һЩ��ͨ�����Եķ�ʽ��õġ���Ȼ��ϸ�����ֵҲ���ܵ�һЩӰ�죬����˵���ʧЧӰ��ή��ϵ����ʣ�����оƬ��ƹ�����Ҳ����Ҫ���Կ��ǡ�

������һ������CPU�Ĺ��ܰ�ȫ���ʾ�������Ҫ����ASILD�ȼ�Ҫ������Ҫ��ϵͳ��ʧЧ�����Ӳ��ʧЧ�бȽϺõĿ��ơ���ô��ʵ��CPU������ô���أ��Ƚ�ͨ�õļܹ���˫��������Lockstep���ṹ��

�ڴ˽ṹ�£���Ȼ����ʹ��������CPU�ںˣ��������������ǵ��˵����ܣ��������洦��ͨ�������ԱȽ�����CPU������������֤��CPU����������ȷ�ԡ�������ƿ������ܼ�����ʵ�ʲ�������Ҫ���Ǻܶ����ء�����Ϊ�˷�ֹ���ʧЧ��Ӱ�죬��Ҫ����“�칹”����ƣ�����˫���ڲ��ṹ���칹��ִ��ʱ����칹������λ�õ��칹�ȡ������Ҫ����������������ȴ�ʩ���Ӷ���֤����CPU�ں˽��ж��������㴦�������ʾ�������������CPU���ܰ�ȫʱ��һ�����ͷ�ʽ��������Ʒ�ʽ������������оƬ�нϳ����ã��ڸ�����оƬ�����Ҳ��������Ƶķ�ʽ���д�����

���������ǿ�һ�°�ȫ�������㣬�ⲿ����Ҫ������Ӳ��ʧЧ����Բ�ͬ��ASIL�ȼ�Ҫ������һ��Ҫ���ǽ����Ӳ��ʧЧ������һ����Χ�ڣ�����ͬʱ���㵥����϶�����DZ�����϶��������Ӳ��ʧЧĿ��ֵ��Ҫ���ڶ���ָ�꣬�ڱ������зdz������Ĺ�ʽ��Ҳ��һЩ���ӣ�����ʵʩ�����ѶȲ������Ǽ����������Ҫȷ��һϵ�в���ֵ����Щ������ȷ�����ǹ��ܰ�ȫ���������е��ѵ㡣

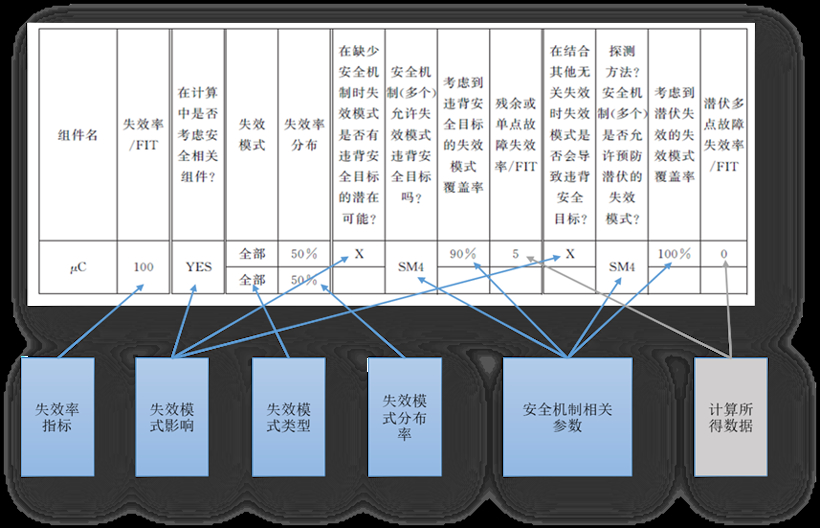

����ͼ��ʾ����Щ�����еIJ��������˻���ʧЧ�ʡ�ʧЧģʽ���塢ʧЧģʽ�ֲ�����ȫ���Ƹ�����������ֵ�ȣ�������Щ���ݵĻ�ȡ����Ҫ���ۺ�֤��֧�ţ���Щ������Ҫͨ���������Եõ���

������˵����Ի���ʧЧ�ʣ�ͨ����Ҫ���������Ի���ʧЧ�ʺ�˲̬ʧЧ�����֡��������������͵�ʧЧ������Ҫ�ڶ�������������Կ��ǡ����������Ի���ʧЧ�ʣ�ͨ�������ַ�ʽ��ȡ����һ�ַ�ʽ��ʹ�û������ҵ��Դ���������Ի���ʧЧ�ʣ��ڶ��ַ�ʽ��ʹ���ֳ�����ͳ�Ƽ��������Ի���ʧЧ�ʣ������ַ�ʽ�Ǵ�����������Ƶ���õ�ʧЧ�ʡ�ͨ����˵����һ�ַ�ʽ��ȡ�����ݻ�Ƚϱ��أ����ô��Ǽ���ʵʩ������ֱ��ͨ����ȡ����ȡ��Ϣ����Ҳ��ҵ��ʹ�ñȽ϶��һ�ַ�ʽ���ڶ��ַ�ʽ�Ѷ�����Ҫ�ռ��㹻���ֳ������������������������֣�������ͳ�ƽ���ͻȷ����������Ҫ�����ض������飬��˻����ӳɱ����������ڡ�����˲̬ʧЧ��һ�����ǻ��ص㿼��α���Ӻ����ӵ�Ӱ�죬������JESD89A������IJ��Է�������˲̬����ʧЧ�ʽ��в�����

����оƬ���ܰ�ȫ�����еĵ�����������֤��ȷ�ϡ������Ƕ������������㲿�����ǰ뵼�壬���ܰ�ȫ��֤��ȷ�϶��DZز����ٵĹ��̣�����Ҫ��Ӧ��“Vģ��”���Ҳࡣ�ӹ��ܰ�ȫ������Կ�����Part 5����Ӳ�����ֵ�Ҫ��Ҳ�����ڰ뵼��㼶�������߲顢���Ͱ�ȫ�����ķ�ʽ�⣬�����ԭ����֤Ҳ��оƬ������������Ҫ���ֶΡ�Ϊ����֤�뵼�弶Ӳ����ȫҪ��ʵʩ�������Ժ���ȷ�ԣ�Ӳ�����ɲ�����Ҫ����ISO 262626:2018-5��ISO 262626:2018-11�е�Ҫ�������ҷ����ἰ�˹��ܰ�ȫ����������ʵ�����ǽ��й��ܰ�ȫ��Ƶ�һ����㣬Ҳ������˵ֻҪ�����Ҫ��Ϳ����ˡ����е�Ҫ������͵�Ҫ���������Ǽ����IJ��ϻ��ۻ��������ȱ����߸�ȫ���Ҫ�Ӷ�ָ�����ǽ�����ơ�

��̸һ�¹���ע�룬����������ڹ��ܰ�ȫ����Ӧ�ý϶࣬�ڰ뵼��������Ϊ��Ҫ������ע�������֧���������ڵ����ɻ������Ӳ��������������ȫ���Ƶ���ϸ���������������̽��ʱ��������Ӱ��ʱ����������������Ӱ���ȷ�ϵȡ�ͨ��������EDA���滷����ʹ�����ּ�����һЩ����Ϊ����оƬʵ�忪�Žӿںͷ�װ����ʽ�����ƣ����������Ĺ���ע����ܵ�һЩ���ơ�ͨ��EDA������Ҳ�Ἧ��һϵ�й��ߣ����������Ƿ����ʵʩ�����IJ�����

���ܽ�һ�£�������������ϵͳ���ܰ�ȫҪ��IJ���������������ɿ��Ե�ͬʱ���Գ���оƬ��ȫ�Ե�����Ҳ�ڲ��ϼ�ǿ�����з��Ϲ��ܰ�ȫҪ���Ѿ���Ϊ�˺ܶ��оƬ“����”�����ԡ��������Ӹ��Ӷȵ�����Ҳ�����˶���оƬ�ĸ���Ҫ�������������������߰�ȫ�Գ���оƬ��ؽ�������“������”���⣬�����Ҫ�Լ����ѹؽ��й��ˣ��������ܽ�ͻ��۾��顣

δ�������Զ���ʻ�����ķ�չ��������оƬ�Լ��ɱ�������ڳ��˵�Ӧ�ò��ϼ�ǿ����֤����оƬ�������Ĺ��ܰ�ȫ�������Ҫ���DZ�Ȼ�����ơ����ܰ�ȫ�����Ȼ�����˰�ȫ�ԣ������ɴ�Ҳ������оƬ�з��ɱ��Լ��۸���������������������оƬ��ʱ���������һ��ѡ����Ƴ�һ�����������г�Ҫ���оƬ������Ԥ�ڹ��ܰ�ȫ��Ϊ�Թ��ܰ�ȫ�IJ��䣬�����˳��������尲ȫ�ԡ���ν�Ԥ�ڹ��ܰ�ȫ�빦�ܰ�ȫ�ںϣ�����оƬ�㼶������ʵ�֣�Ҳ��δ����Ҫ˼���ͽ�������⡣

���ݽ������ݾ�����Щ�����ܸ�ƫ���ڼ�������һЩ��ϣ���ܸ���Ҵ���һЩ�ջ�лл��ҵ�ʱ�䣡

������������վ���ش��Ľ�������Ϣ������������ζ����ͬ��۵㼰�����������е���Ȩ��Ϊ���������Ρ����漰��Ȩ�����⣬����������ϵ����ϵQQ��26887486�������ǽ���ʱɾ��������

�������ӣ�https://www.huangheauto.com/article/14/13722.html